垂直腔面发射激光器(VCSEL)的制备

北京工业大学

吕朝晨

1、引言

随着苹果公司iPhone X的热卖,iPhone X的Face ID面部识别功能在手机消费市场引起了巨大反响,Face ID面部识别功能是一种基于3D深度视觉技术的应用,该项应用其实早已出现于微软Kinect、英特尔RealSense等消费级产品中。3D摄像头相比传统摄像头最大的区别就是在前端引入了垂直腔面发射激光器(VCSEL)模组,3D摄像头既能够获得平面图像又能够获得拍摄对象的景深信息,使其能够实现实时采集三维信息。其实这些功能都得益于VCSEL激光器。

VCSEL全称为垂直腔面发射激光器(Vertical cavity surface emitting laser),相比于传统的边发射激光器和发光二极管(LED)有以下优点:阈值电流小、光垂直于衬底面出射易于二维集成、近场和远场光斑呈圆形对称易于光纤耦合、发散角小、调制速率高等。VCSEL除了3D感测领域的应用外,最多还是应用光通信领域。应用于短距离光互连的高速光收发模块的发射光源便是VCSEL。BCC Research公司的分析师认为,目前全球VCSEL的总收入已接近8亿美元,预计到2020年该值会增长到21亿美元。VCSEL的应用主要由短距离光纤数据传输链路的部署所主导,这部分市场大约占据了VCSEL市场近一半的份额[1]。除了这两项主要的应用外,VCSEL还在原子钟、气体检测、激光雷达、激光打印等方面有着很大的前景。接下来我将讲述我们课题组关于光通信和3D感测用VCSEL的制备工艺及相关测试。

2、VCSEL的制备

2.1 VCSEL外延生长

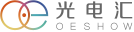

在VCSEL外延结构生长过程中,我们使用华芯半导体科技有限公司Veeco的TurboDisc K475i As/P MOCVD 系统,以4寸的半绝缘 GaAs(110)作为外延材料生长衬底,以三甲基镓(TMGa)、三甲基铝(TMAl)、三甲基铟(TMIn) 作为Ⅲ族源,砷烷(AsH3)作为V族源, 硅烷(SiH4)作为n型掺杂源,四溴化碳(CBr4)作为p型掺杂源。生长过程中为了降低衬底外延缺陷或杂质向下限制层的扩散,确定缓冲层GaAs的厚度为 500nm。DBR中AlGaAs和有源区的InGaAs在外延生长时需要精确控制生长温度、气体流量、时间等条件,使各元素组分满足设计要求[2]。VCSEL全结构共200多层,总厚度只有不到10微米,需要先长出每一种单层,通过各种测试设备确认单层的质量、组分、载流子浓度和生长速率等,再一次外延出整个全结构。如图1所示VCSEL外延结构(SEM扫描电子显微镜)。

图1 VCSEL外延结构(SEM扫描电子显微镜)

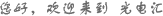

通过优化气流模型,使得满盘(4寸*15片)外延片波长均能达到spec要求,F-P腔模波长平均值850.97nm,满盘波长标准差0.17%,完全能够满足量产需求,并且大大降低了芯片成本。如图2所示满盘腔模波长均匀性。

图2 VCSEL满盘生长腔模波长均匀性

生长出外延片后需要经过全自动荧光光谱仪(PL)测试VCSEL的白光反射谱确认dip位置确保激射波长在预测范围内;然后经过电化学C-V测试系统(ECV)测试半导体材料及外延层材料浓度纵向分布;再经过原子力显微镜(AFM)测试外延片表面形貌,判断外延片质量。

2.2 VCSEL芯片制造

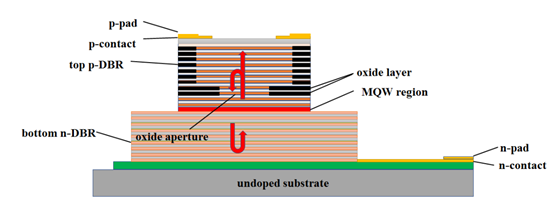

VCSEL器件结构如图3所示从下往上依次是为衬底、N型接触层、N型DBR层、量子阱层、P型DBR层、P 型接触层。其中P型DBR 层中有两层是高Al组分的AlGaAs 层。两层氧化限制层都采用了30nm的Al0.98Ga0.02As,利用双氧化层结构, 降低了氧化层所引入的电容,从而减小了器件的电子寄生参数[2]。

图3 850nm VCSEL 结构示意图[2]

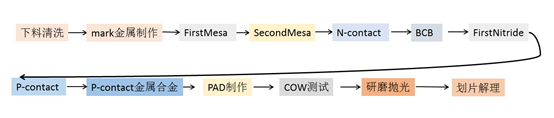

芯片工艺过程包括10次清洗、9次光刻、5次干法刻蚀(包括BCB工艺)、4次金属工艺、1次湿法氧化工艺。各工艺环环相扣,一道工艺的成功与否直接影响下一道工艺的结果。如图4所示VCSEL芯片制备工艺流程:

图4 VCSEL芯片工艺流程图

如下是VCSEL芯片制备的关键工艺:

1)VCSEL湿法氧化工艺

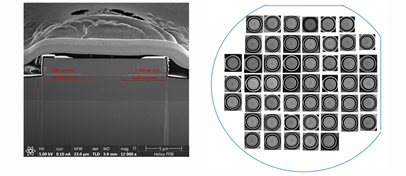

VCSEL氧化孔径尺寸及均匀性直接影响器件的性能和成品率,特别是4×1 Array,12×1 Array。氧化孔径的大小和形状决定着VCSEL器件的很多性能参数,如VCSEL的阈值电流大小、光功率大小、串联电阻大小、-3dB带宽大小等。湿法氧化工艺直接提高了VCSEL作为商用器件的技术难度,精确控制氧化孔径尺寸及氧化孔径形状成为其工艺中的主要技术难点。控制氧化孔径大小和氧化孔径形状需要同时在外延和芯片两个技术上进行改进,包括外延控制好氧化层铝组分、纳米级的氧化层厚度和芯片工艺时控制氧化温度、气体流量等重要参数,我司技术人员通过多次工艺改善,成功解决了控制湿法氧化工艺的技术难题,把氧化孔径精度控制在±1μm,且氧化孔径形状大致呈圆形,提高了VCSEL器件的性能和成品率。如图5所示SEM剖面图和采用自制的红外光源显微镜和CCD观测俯视成像系统,将氧化孔径尺寸精度控制在±1μm。

图5 VCSEL氧化剖面图和俯视图

2)精确的台面刻蚀技术

在VCSEL台面刻蚀过程中,精确控制刻蚀深度非常重要,我们在刻蚀过程中引入了端点监控来保证刻蚀的精确程度,即电感耦合等离子体发射光谱仪。精确控制各台面的刻蚀深度,保证后续工艺的进行。比如,第一台面必须刻蚀到设计好的有源区以下3对DBR外延层附近,多刻蚀或者少刻蚀都会给后续工艺带来灾难性的影响,在ICP刻蚀工艺时,多次调整其刻蚀均匀性、刻蚀速率,保证整片刻蚀的均匀性。如表1所示用台阶仪监控刻蚀深度。

表1 VCSEL 第一台面五点刻蚀深度[2]

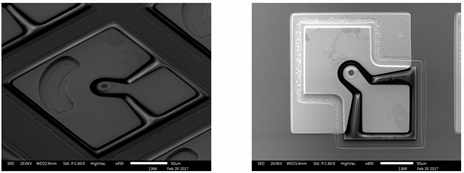

3)独特BCB平坦化工艺制程

在VCSEL工艺中,我们引入BCB(苯并环丁烯)作为各台面刻蚀的填充介质,BCB在填充台面的同时还会降低VCSEL器件电极间的寄生电容,提高其高速调制性能,由于刻蚀深度略大导致需要BCB匀涂的厚度非常大,16μm厚的BCB胶在图形转移时容易出现图形走样,坍塌等情况,故较厚的BCB进行图形转移和平坦化就增加了其工艺难度,通过工艺摸索,成功掌握了BCB平坦化及图形良好转移的技术要点,并通过生产验证,如图所示,SEM扫描电镜下带BCB的VCSEL器件。如图6所示SEM下加BCB电子树脂的芯片外貌。

图6 SEM下加BCB电子树脂的芯片外貌

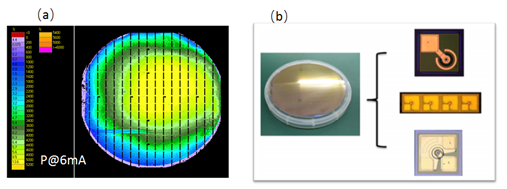

完成一系列芯片工艺后,我们会进行在片测试,然后根据测试情况按不同的参数要求用分选设备进行分选。如图7所示VCSEL测试6mA下光功率和解理后产品。

如图7所示(a)VCSEL测试6mA下光功率和(b)VCSEL解理后产品。

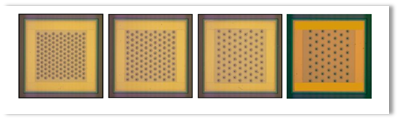

3D感测类VCSEL与光通信VCSEL制造工艺相似,在这里就不一一叙述了,如图8所示3D感测类VCSEL芯片产品图。

图8 3D感测类VCSEL芯片产品

2.3 VCSEL芯片测试

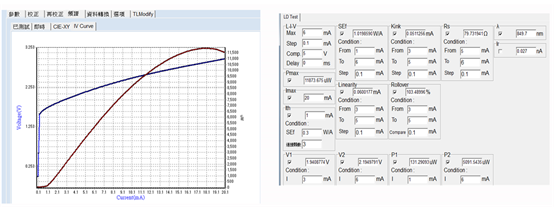

高速 VCSEL 器件静态特性和动态特性表征了 VCSEL 器件的整体性能, 在静态特性测试方面, 采用 VCSEL 静态测试系统, 该系统有两个铍铜正负极探针,测试时调节探针控制器,使探针接触到 VCSEL 芯片正负极电极,通过调节电流源注入 0-20mA 电流, 由积分球接收激光并得出测试结果.如图9所示VCSEL L-I-V测试结果,峰值功率可达11mW,斜效率达1.01W/A。

图9 VCSEL L-I-V测试结果

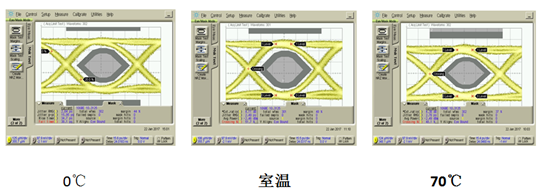

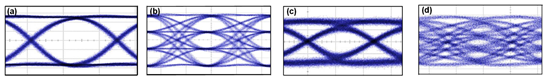

VCSEL封装成10 Gb/s TOSA后测试,不同环境温度下脉冲大信号眼图对比,如图10所示。图11所示NRZ 25G VCSEL 测试眼图及25Gbaud PAM4眼图[3]。

图10 不同环境温度下10Gb/s TOSA脉冲大信号眼图对比

图11 (a)(b)标准电眼(c)(d)经VCSEL调制后的光眼图

[1] http://www.eepw.com.cn/article/201709/364215.htm.

[2]吕朝晨,王青,尧舜,周广正,于洪岩,李颖,郎陆广,兰天,张文甲,梁辰余,张杨,赵风春,贾海峰,王光辉,王智勇. 4×15Gbit/s 850nm垂直腔面发射激光器列阵[J].光学学报,2018,38(5):0514001.

[3] S Yao,Z Lv,W Zhang,Q Wang,C Liang,Mass-production Level 200-Gb/s 850nm VCSEL Arraywith up to 1.03-W/A Current-Light Slope Efficiency,OSApublishing,acp2017.

浏览量(2419)

浏览量(2419)